(V00.29)

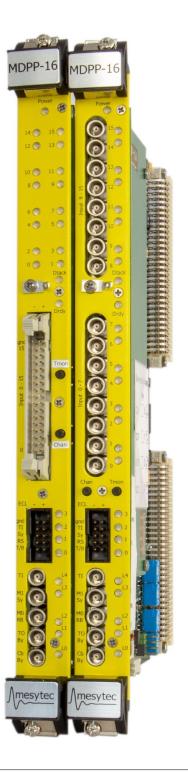

16 channel VME pulse processor

mesytec **MDPP-16** is a fast high resolution time an amplitude digitizer. It is internally realized as a 16 channel adjustable low noise amplifier and a variable differentiation stage, followed by filters and 80 MHz sampling ADCs. The digitized data are analyzed in an FPGA and reconstructed with highest precision. This allows to achieve unique timing and amplitude resolution.

# Hardware features:

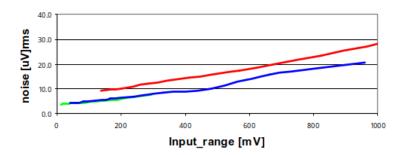

- Low noise variable gain input amplifiers.

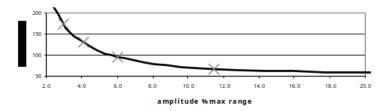

- Input signals for maximum range (highest spectrum channel) from 1.5 mV to 20 V.

- Input noise down to  $2 \mu V @ 2 \mu s$  shaping.

- Variable hardware pre-differentiation

Allows large offsets and signal stacking without effect on the amplitude or timing resolution.

• Reset stage (supports reset preamplifiers)

Dynamical range for reset preamps: reset pulse / noise =  $1.5*10^6$  at 2us shaping time. Recovery within 2  $\mu$ s + shaping time.

• Gain-polarity jumpers

determine: termination, polarity, input range and input configuration (differential / unipolar).

• Two high resolution monitor outputs

for monitoring internal signals and noise via oscilloscope.

• Two high resolution trigger inputs

24 ps resolution, start window, add time stamp

- One high resolution trigger output (1.5 ns resolution)

- Up to 4 software modules

can be stored on board and can be selected by switch or VME.

- Installation and update via USB or VME

- VME64X format, downward compatible to VME64

- SCP and QDC softwae allow to add sample trails up to 1000 samples

# Software modules

Large digital resources allow precise wave form reconstruction.

- timing down to 60 ps rms

- amplitude resolution better than **32k**.

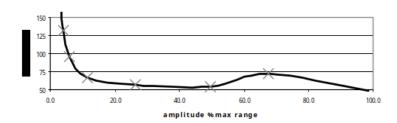

- Trigger threshold down to 1/3000 of maximum range.

#### FPGA software modules:

- Amplitude & time for standard preamps (SCP), 64 k/60 ps

- Amplitude & time for reset preamps (RCP) 64 k/60 ps

- QDC: charge & time & PSD, self gating, 64k/60 ps

- Peak sensing ADC, 64 k, self gating or external

- Pulse shape discrimination for CsI Scintillator

# For MDPP-16 the following software is available:

#### **SCP = Signal Processing of Standard Charge Integrating Preamplifiers**

Outputs:

Amplitude 64k,

Timing 64k channels with min 24ps

From Revision FW2050 can transmit up to 1000 samples per channel

# RCP = Signal Processing of Charge Integrating Preamplifiers with Reset

Outputs, typically germanium detectors;

Outputs:

Amplitude 64k,

Timing 64k channels with min 24ps

#### QDC = Signal Processing of fast PMT signals without preamp.

Pulse Shape Discrimination, timing

Outputs:

Amplitude Short 64k,

Amplitude Long 64k,

Timing 64k channels with min 24ps

From Revision FW3050 can transmit up to 1000 samples per channel

# **PADC** = **Peak sensing ADC. Signal Processing of Shaped Signals.** Peak sensing ADC with Baseline Restorer, self triggering. The peak maximum is used to determine a high quality timing.

Outputs:

Amplitude Long 64k,

Timing 64k channels with min 24ps

#### **CSI = Signal Processing of Standard Charge Integrating Preamplifiers**

calculates short shaped amplitudes and long shaped amplitudes and Timing. Typical signals from CsI scintillator light with PMT and Charge preamp, Signal from 3He tubes for n-detection. Pulse shape discrimination of Si-Detector signals.

Outputs:

short integrated Amplitude 64k, long integrated Amplitude 64k,

Timing 64k channels with min 24ps

# Hardware concept of MDPP-16

**MDPP-16** was developed to meet the following challenges:

- 1. Easy to use:

- No knowledge of the internal signal processing required.

- Only essential signal parameters and settings required for operation.

- Input is capable to directly accept any preamplifier signal.

- 2. **Works together with existing VME modules -** accepts and creates triggers for an external experiment logic.

- 3. **Provides very good timing -** good enough to replace external CFDs and TDCs for most applications.

- 4. **Amplitude resolution as good as best analog solutions,** including ballistic loss correction, pile up rejection (reconstruction), baseline restoration.

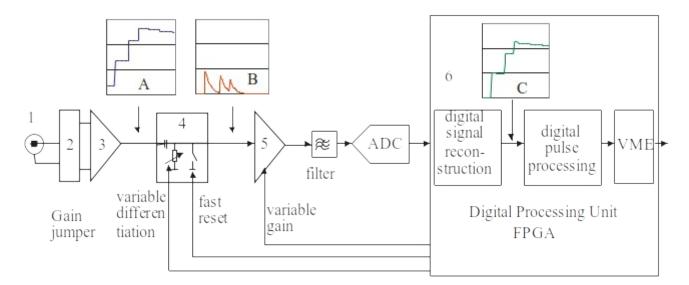

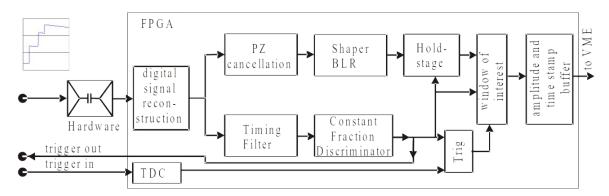

To meet those goals, a new hardware concept was required as shown in the following figure.

The input (1) was designed to allow two configurations:

- differential and unipolar input with a standard 34 pin header connector (depending on applied jumpers).

- Unipolar input with Lemo inputs.

The input signal amplitude for maximum output range is from 1.5 mV to 20 V and can be set by different input jumpers (2), a variable gain stage (5) (gain 1 to 24) and by additional scaling of the digitized data (6). So a continuous gain from 1.00 to 200.00 is provided for each gain jumper set.

The input is followed by a high dynamic range, **low noise amplifier (3).** Its signal is then differentiated by an adjustable **differentiation stage (4)**. It is part

of the shaping filter, and is set by the central logic unit. It also includes a fast reset circuit, which allows fast recovery from large overflow and underflow signals. It delivers an output which is **free of offset** (B) and eliminates the typical **stacking** (A) of charge integrating preamplifiers. So the dynamic range of the ADC can be fully used.

The digital processing unit (6) can be loaded with different software programs (up to 4 may be stored on board). With "SCP" software module for processing of charge sensitive preamp signals, the ADC signal is regenerated by an integration and the signal input (without offset) is fully recovered (C). Then the signal is processed with high precision and the help of 180 signal processors. Details of processing are described at another place with the software modules.

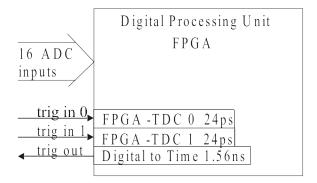

The MDPP-16 provides **further resources** to allow easy integration into a standard nuclear physics data acquisition system. It provides two high resolution trigger inputs (24 ps timing resolution). One of them may start the window of interest, while the other may add an additional time mark from an external detector.

Internally created triggers from the 16 input channels can be output to a high resolution trigger output (1.56 ns resolution). This allows to create an external experiment trigger from many modules. The trigger delay is typically 400 ns (+ TF-integration time) from the edge of analog input signal.

The externally created trigger can then be fed to one of the trigger inputs to start the widow of interest. There are no problems with delay between trigger and channel input data, because the window of interest can be shifted in time by up to +-25 us.

# Get sample trails

"SCP" and "QDC" software. Starting from Package SP0043

In the updated software packets "SCP" for charge integrated signals and "QDC" for direct PMT and similar high gain sources, an extension is implemented allowing to add up to 1000 sample values per channel (12.5us trail length). For a trail length of up to 500 samples, two traces per channel can be registered simultaneously, minimising the channel dead time. It is possible to specify a number of pre samples (before the input signal edge) and any number of samples (up to 1000) required. Up to 80 M Samples/s can be transmitted to the VME bus when 2ESST readout mode is used. This results in up to 320 MBytes/s of data transferred via VME bus.

The sample trails are simply added to the channel data. The powerful trigger system via window of interest, internal/external triggering is unchanged. The high resolution timing and amplitude(s) are emitted simultaneously.

Sample source can be set to direct ADC signal, and to several internally processed signals.

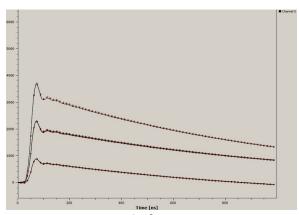

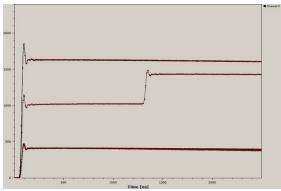

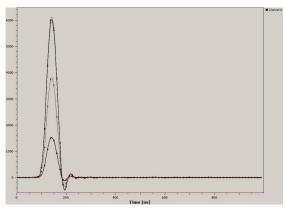

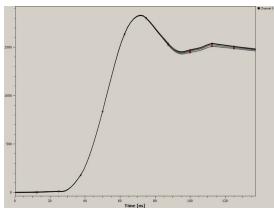

The following pictures show sample trails from "SCP" software with different sources selected. They can be displayed by myme software in "event history" display.

Directly from ADC

ADC signal after first deconvolution

Timing Filter output, triangular shaped

Triangular shaper signal for amplitude

# Resampling

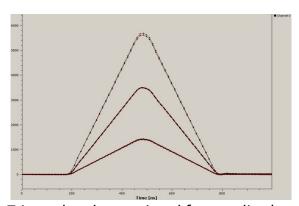

Usually the input signals are asynchronous to the sampling frequency. This results in a jitter of the digitized signal by the sampling period in time. To get a stable display there are two possibilities:

1) MDPP can do a resampling. So it calculates new sampling points related to the precise time measured by the digital discriminator in the timing path.

2) In the sampling header, a "phase" showing the time difference between discriminator time and sample time is transmitted. In the myme display the curve is shifted by this time to give a stable display as usually shown by an oscilloscope.

Display of 20 traces without resampling

Display with resampling in MDPP-16

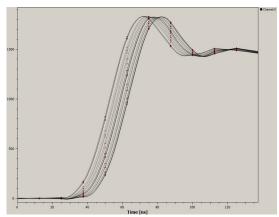

# **Interpolation / reconstruction**

A sin(x)/x interpolation (order 6 is used here) of traces requires four samples before and 3 samples behind the interpolated time slice between two samples. So in the mvme display (first approach) the first 3 and last 3 samples are interpolated linear. So for a time slice to be precisely interpolated there are 6 neighbour samples needed.

That's not required for resampling in MDPP-16. For the integrated resampling filter any number of samples is available. So for data reduction it is even possible to transmit only two samples to determine the rise time of a signal.

#### Offset correction

The 4 samples before transmitted samples are used for offset subtraction: mean value of the 4 samples is subtracted from all following samples.

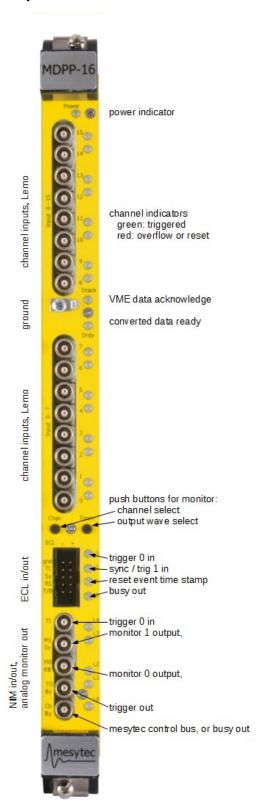

# Front panel elements

MDPP-16 provides 16 bi-color LED indicators for each channel. When lighting green the signal is within the legal range, red indicates an under- or overflow. When a channel is selected for monitoring, the LED flashes red.

There are two push buttons on the front panel to control the monitor function. One selects a channel to monitor, the other one selects a pair of wave forms

The wave forms reflect signals generated in the pulse processing chain inside the FPGA. The signals are output at two Lemo connectors (L2, 3)

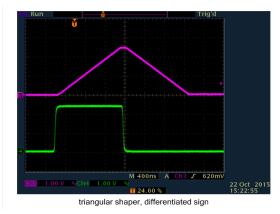

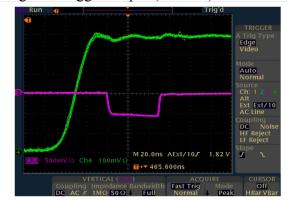

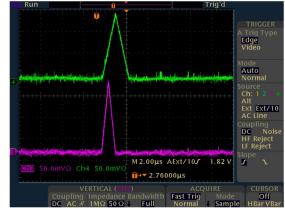

The following oscilloscope picture shows a wave form pair:

The green curve shows the differentiated signal. The magenta one shows the integral of the differentiated signal, creating the typical triangular shaping curve.

Also strongly amplified wave forms can be selected to monitor the structure of external noise.

#### Monitor signals: mon0 / mon1

- 1. raw data / reconstructed signal

- 2. TF-output / Shaper output

- 3. Shaper x 32, BLR-signal x 32

- 4. Shaper x 32, Timing Filter x 32

# Timing and data concept - "Window of interest"

The window of interest concept is the same as for MQDC-32 and MTDC-32.

MDPP-16 creates an output trigger from any selected input channel or by a logical "or" of all or some user selectable channel inputs. The output trigger has a timing resolution of maximum 1.56 ns.

It is intended to feed a trigger logic in more complex setups.

MDPP-16 then expects an external gate from external trigger logic, which is evaluated with a high resolution (24 ps) time to digital converter (TDC).

In the simplest configuration, output trigger can be fed back to the trigger input to allow self triggering. The input trigger can be shifted internally by +/-25 us and starts a **window of interest** with adjustable width (1.5 ns to 25 us). All triggers generated by the CFD discriminators from the channel inputs, which fall into this window, are sent to a large data buffer for read out by The VME bus. The transmitted data are:

- the time difference to the window start (in 24 ps resolution)

- the converted shaper amplitude.

- over/underflow, and pileup flags

The provided buffer structure and all features like Event time stamp, event counter... are identical to all other mesytec VME-modules.

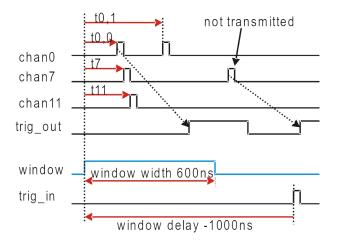

#### **Example:**

In the example, the internal triggers of three input channels are shown after the CFD discriminator.

Two pulses are detected in channel 0 and 7, one in channel 11. The very first pulse, which is in channel 0, starts the output trigger. This trigger may be fed through an external electronics and - if coincident to other detectors and data acquisition is not busy - returns delayed to the trigger input. It arrives with a fixed delay of 800 ns. So it has to be shifted back in time by MDPP-16 (here 1000 ns) and a coincidence time (window with) of 600 ns has to be created. As can be seen 4 hits fall into this window (2 x channel 0, 1x channel 7 and 11).

So four time differences referenced to the window start are calculated, and are sent to a data buffer together with the according amplitudes.

#### All software modules have the following features:

- Support different types of event synchronisation stamping (based on VME-clock or external clock)

- Multiplicity filter, selects events in specified multiplicity range

- mesytec control bus to control external mesytec modules

- Address modes: A24 / A32

- Data transfer modes: D16 (registers)

- D32, BLT32, MBLT64, CBLT, CMBLT64

- Multicast for event reset and time stamping start

#### Hardware features

- Live insertion (can be inserted in a running crate)

- Power consumption: 14 W,

- + 5 V, 2 A

- + 12 V, 100 mA

- 12 V, 200 mA.

# Software module: "SCP"

(Delivers timing and amplitude for **standard charge sensitive preamplifier** signals) Replaces shaper, peak sensing ADC, timing filter amplifier, CFD, and TDC.

The following picture shows a schematic representation of the software:

The signal is amplified filtered digitized and reconstructed as described in the hardware chapter. Then it is split into a timing branch, and enters a **timing filter**. It differentiates and integrated the signal with short adjustable time constant. Then a digital **CFD** (discriminator) calculates an amplitude independent time trigger (=time stamp).

In the other "slow" branch the signal is deconvoluted (**PZ cancellation**) and then enters a filter consisting of a differentiator and integrator forming a filter, which produces a **triangular shaping**. Also a **base line restorer** is implemented.

Then signal then enters a **hold stage** which holds the amplitude at a well defined time, determined by the CFD discriminator.-

Then the amplitude and timing values are filtered by a **window of interest** and stored in a **buffer**.

#### **Short data:**

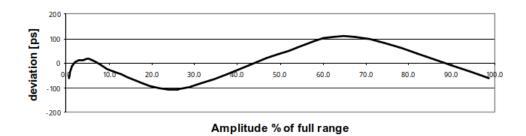

- Amplitude resolution of up to 32 k (15 bit)

- Trigger to channel time resolution of **60 ps rms**, uniform at any delay.

- Channel to channel time resolution of **60 ps rms**, uniform at any delay.

- Trigger input with 24 ps timing resolution

- Extreme dynamic range (trigger 3000:1)

- Independent shaping of timing filter and amplitude branch.

- Shaping width can be set from 50 ns to 25 μs FWHM (= 25 ns to 10 us sigma values) in steps of 12.5 ns.

- Timing filter from 15 ns to 1.6 us.

- Can be operated self triggered or externally triggered

- Outputs internal raw trigger with 1.5 ns time resolution

As easy to operate as all mesytec modules and fully data compatible.

# Only five parameters have to be set:

# Signal properties:

- 1. signal rise time 15 ns to 1.6 μs (= TF integration and diff-time)

- 2. signal decay time (for PZ) 800 ns to  $\infty$ .

- 3. Gain 1 to 200 in steps of 0.01

#### **User settings:**

- 4. Shaping time: 25 ns to 11 μs (50 ns to 25 μs FWHM)

- 5. Threshold

#### **Output Data**

channel 0..15 Amplitude (11 to 16 bit) channel 16 to 31 time difference to window start (16 bit) 24 ps/chan.

# **Monitor outputs**

(Lemo 2 = mon 0, and Lemo 3 = mon 1)

Switching on the monitor: press pushbutton "chan", then select a waveform with "Tmon" button. The button "chan" allows to switch through the individual channels.

#### Wave forms:

#### Tmon 0,

Green: preamplifier signal before ADC, Magenta: trigger output (Lemo 1)

Input signal, Trigger output

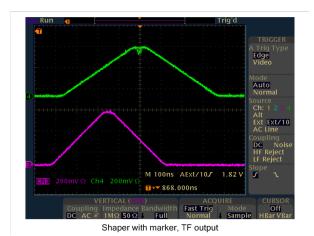

# **Tmon 1:** Check signal **shape and amplitude** Green: mon 0, triangular shaped signal with flicker mask, showing the sampling time. Magenta: mon 1, timing filter signal

#### restorer

Green: mon0, Shaper signal amplified x32. Magenta: mon 1, reconstructed baseline by the baseline restorer, x 32

Shaper x 32, reconstr. Baseline x 32

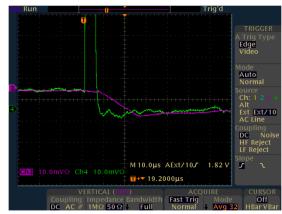

# Tmon 3: Check noise

Green: mon 0, Shaper signal, baseline restored x32Magenta: mon 1,timing filter signal x 32

Noise inspect, Shaper, Timing Filter

Tmon 2: Check pole zero adjust and baseline

# **Control input / output**

- Differential control inputs:

- interface any differential signals: ECL, LVDS or LVPECL. They can be individually

- terminated (110  $\Omega$ ) via register setting

- NIM inputs:

- standard NIM, 50  $\Omega$

- NIM output:

- -0.7 V when terminated with 50  $\Omega$

- mesytec control bus output, shares connector with busy output. +0.7 V terminated

Minimum trigger width for individual inputs is = 10 ns Maximum external reference synchronisation clock frequency (sync input): 75 MHz

Digital Inputs /outputs (see IO register block 0x6060) and description

# **Setting VME base address:**

For setting the address of a module, it is easiest to only use the 8 high bits of the address (two high bit hex coders on the mother board) and leave the lower 8 bits at 0,0..

The 8 high bits also automatically occur in the event header.

For VME64X modules in a VME64X crate, the geo coding can be used by setting the 4 address coders to F,F,F,F. The the slot number is then used as module address.

For example Slot 15 will create the base high address 0x0F00.

# MDPP-16 register set, SCP Firmware (processing of Standard Charge sensitive Preamp signals) Data FIFO, read data at address 0x0000 (access R/W D32, 64)

only even numbers of 32 bit-words will be transmitted. In case of odd number of data words, the last word will be a fill word (=0).

FIFO size: 48 k - 1 k = 48128 words with 32 bit length

# Header (4 byte)

| 2<br>header<br>ignature | 2<br>subhea<br>der | 3    | 1<br>SA | 8<br>modul<br>e id | 3<br>TDC_resolution<br>→ 0x6042 | 3    | 1<br>number of following<br>data words, including<br>EOE |

|-------------------------|--------------------|------|---------|--------------------|---------------------------------|------|----------------------------------------------------------|

| b01                     | b00                | b000 | 0       | modul<br>e id      | bxxx                            | bxxx | number of 32 bit data<br>words                           |

When Sampling mode is active:

| b01 | b00 | b000 | 1 | modul<br>e id | 16 bits, number of 32 bit data words |

|-----|-----|------|---|---------------|--------------------------------------|

#### Data (4 byte) DATA event

| 2        | 2  | 4    | 2         | 1       | 5       | 16        |

|----------|----|------|-----------|---------|---------|-----------|

| data-sig |    |      |           |         |         |           |

| b00      | 01 | VVVV | (pu ov)*  | Trigger | channel | ADC value |

| 000      | 01 | XXXX | (pu, ov)* | Flag    | number  | ADC value |

channel numbers may come in arbitrary order. \* pu = pile up flag, ov = overflow or underflow flag

# Data (4 byte) DATA event

| 2<br>data-sig | 2  | 6     | 1               | 5                         | 16                  |

|---------------|----|-------|-----------------|---------------------------|---------------------|

| b00           | 01 | xxxxx | Trigger<br>Flag | channel<br>number<br>+ 16 | TDC time difference |

# Data (4 byte) Extended time stamp

| 2        | 2  | 12             | 16                         |

|----------|----|----------------|----------------------------|

| data-sig |    |                |                            |

| b00      | 10 | XXXX XXXX XXXX | 16 high bits of time stamp |

# Data (4 byte), fill dummy (to fill MBLT64 word at odd data number)

| 2        | 30 |

|----------|----|

| data-sig |    |

| b00      | 0  |

#### **End of Event mark (4 byte)**

| 2   | 30                         |

|-----|----------------------------|

| b11 | event counter / time stamp |

Taking the trigger flag and channel number together, this 6 bit address runs from 0 to 15 for amplitudes, 16 to 31 for time, and 32 / 33 are trigger 0 / trigger 1 time.

So the full channel address has 6 bits, and runs from 0 to 33. The addresses 32 is for trigger input 0, the address 33 for trigger input 1.

# Sample Transmission

From QDC Firmware packet FW3050 and SCP packet FW2050, samples can be added to the data stream. Enaable "sampling" is done with register 0x6044, pre-samples, total samples, and sorce have to be specified. Note that the event header has a 16 bit data length field in sampling mode.

Samples follow the time word (order: Amplitude, time, sample header, samples, Amplitude of next channel)

| 2        | 2   | 6                                  | 6                      | 16                  |  |  |

|----------|-----|------------------------------------|------------------------|---------------------|--|--|

| data-sig |     |                                    |                        |                     |  |  |

| b00      | b01 | xxxxxx                             | channel<br>number 1631 | TDC time difference |  |  |

| b00      | b11 | Sample header[27:0]                |                        |                     |  |  |

| b00      | b11 | Sample1[13:0], Sample0[13:0]       |                        |                     |  |  |

|          |     |                                    |                        |                     |  |  |

| b00      | b11 | Sample_2N[13:0], Sample_2N-1[13:0] |                        |                     |  |  |

Sample header: { 0, sample config[7:0], phase[8:0], following sample words[9:0] }

Following sample words[9:0]: (= N) up to 500 sample pairs may follow = 1000 samples.

Phase[8:0]: a phase with range 0 to 511 is transmitted, showing the distance between trigger point to the ADC sampling time. If "resampling" is active this word is not needed. If resampling is switched off, it can be used to shift samples for jitter free display of wave forms.

Sample config[7:0]: { not\_offset, not\_resample, 0, 0, 0, 0, source[1:0]}

source = 0 Samples directly from ADC

**SCP**

source = 1 Samples from reconstructed input signal

source = 2 Samples from timing filter shaper

source = 3 Samples from main shaper

ODC

source = 1 Samples from short integration

source = 2 Samples from long integration

#### Extract samples:

-extract time word, extract channel address from time word

-next word with data[31:28] == 0x3 is the sample header

-following words with data[31:28] == 0x3 are the samples for the detected channel

#### **Samples**

When "sampling" in register 0x6044 is switched on, samples are transmitted following a channel data word. The channel data word provides the channel address.

Then a sampling header is transmitted, followed by sample pairs.

# **Sample Header**

| 2        | 2  | 9           | 9     | 10                     |

|----------|----|-------------|-------|------------------------|

| data-sig |    |             |       |                        |

| b00      | 11 | Config word | Phase | Number of Sample pairs |

Sample data

| 2    | 2    | 14            | 14           |

|------|------|---------------|--------------|

| data | -sig |               |              |

| b0   | 0 11 | Sample second | Sample first |

Format of Sample: 14 bit signed integer (+-8k range)

# Config word = Word set in register 0x614A

| 0x614A | sample_config | 9 | RW | 0 | {0,no_offset_corr, no_resamp,0,0,0,0,source[1:0]} |

|--------|---------------|---|----|---|---------------------------------------------------|

|        |               |   |    |   | source                                            |

|        |               |   |    |   | source = 0 Samples directly from ADC              |

|        |               |   |    |   | source = 1 Samples reconstructed input            |

|        |               |   |    |   | source = 2 Samples from TF-Shaper                 |

|        |               |   |    |   | source = 3 Samples from Shaper                    |

For MDPP-16: when the number of samples is 500 or less per channel, two samples can be recorded simultaneoulsly per channel. So sample recording does no block the channel. So for most cases, the sample recording does not add dead time to a channel.

# SCP and QDC software allows two "streaming modes" from Firmware revision SCP\_FW2050 / QDC\_FW3050.

Setting Register 0x6044 to 4 switches on compact streaming mode, 0x6044 = 8 the standard streaming mode. In streaming mode the timing of MDPP-16 is synchronised to the VME backplane clock.

All 16 channels and the 2 trigger inputs are now completely independent and output an independent event frame. Window of interest is switched off.

In streaming mode, the module is synchronised by the VME backplane clock. So all modules in one crate run synchronous. When time stamp counter is reset by a VME multicast reset to all modules, the maximum time offset may be 12.5 ns.

# Compact streaming mode:

The event frame is always 2 words long.

# Header (4 byte)

| 2<br>header<br>signatu<br>re | 6<br>module id | 6<br>Address[4:0]<br>{trig_flag,0,address} | 2<br>Pile_up,<br>overflow | 16<br>Amplitude |

|------------------------------|----------------|--------------------------------------------|---------------------------|-----------------|

| b01                          | module id      | T0AAAA                                     | P,O                       | Ampl[15:0]      |

For Trigger events (Trig flag (data[21]) is set) the number of events, which were skipped due to buffer overflow since last trigger is emitted in at the place of "amplitude".

# **End of Event mark (4 byte)**

| 2   | 30                                  |

|-----|-------------------------------------|

| b11 | Fine time stamp (set in reg 0x6042) |

#### **Standard streaming mode** (Setting Register 0x6044 to 8)

Has the same data format as standard mode with window of interest, but only one channel -with amplitude

- or trigger (address 0b10000 and 100001, skipped events[15:0])

is emitted in a packet. The "module time stamp" is the precise time stamp set in register 0x6042.

Extended time stamp with extra 16 bits of time stamp (total 46 bits) is possible.

Also sample transmission is possible (0x6044 to 24).

# For RCP-Firmware a reset event is generated for each reset of the preamp

# Header (4 byte)

| 2<br>header<br>signature | 2<br>subheade<br>r | 4    | 8<br>module id | 3<br>TDC_resolutio<br>n<br>→ 0x6042 | 3<br>ADC_resolution<br>→ 0x6046 | 10<br>number of following<br>data words, including<br>EOE |

|--------------------------|--------------------|------|----------------|-------------------------------------|---------------------------------|-----------------------------------------------------------|

| b01                      | b00                | xxxx | module id      | bxxx                                | bxxx                            | number of 32 bit data<br>words                            |

# Data (4 byte) DATA event

| 2        | 2  | 4 | 2 | 6  | 12 | 4                      |

|----------|----|---|---|----|----|------------------------|

| data-sig |    |   |   |    |    |                        |

| b00      | 01 | 0 | 0 | 33 | 0  | Channel index of reset |

# Data (4 byte) Extended time stamp

| 2        | 2  | 12             | 16                         |

|----------|----|----------------|----------------------------|

| data-sig |    |                |                            |

| b00      | 10 | XXXX XXXX XXXX | 16 high bits of time stamp |

# Data (4 byte), fill dummy (to fill MBLT64 word at odd data number)

| 2        | 30 |

|----------|----|

| data-sig |    |

| b00      | 0  |

# **End of Event mark (4 byte)**

| 2   | 30                         |

|-----|----------------------------|

| b11 | event counter / time stamp |

# Registers, Starting at address x6000 (access D16)

| Address | Name              | Bits | dir | default | Comment                                    |

|---------|-------------------|------|-----|---------|--------------------------------------------|

|         | Address registers |      |     |         |                                            |

| 0x6000  | address_source    | 1    | RW  | 0       | 0 = from board coder, 1 from address_reg   |

| 0x6002  | address_reg       | 16   | RW  | 0       | address to override decoder on board       |

| 0x6004  | module_id         | 8    | RW  | 0xFF    | is part of data header                     |

|         |                   |      |     |         | If value = FF, the 8 high bits of base     |

|         |                   |      |     |         | address are used (always board coder).     |

| 0x6006  | Fast MBLT         | 1    | RW  | 1       | Setting to 0 limits MBLT cycle to min      |

|         |                   |      |     |         | 100ns. Else 65 ns are possible.            |

| 0x6008  | soft_reset        | 1    | RW  |         | Write breaks all activities, sets critical |

|         |                   |      |     |         | parameters to default. Wait 200ms after    |

|         |                   |      |     |         | writing this register.                     |

|         |                   |      |     |         | Read: MDPP-16 hardware ID: 0x5005          |

| 0x600E  | firmware_revision | 16   | R   |         | Example: RCP=1, rev 2.4 = 0x1204           |

|         |                   |      |     |         | SCP=2, rev 1.2 = 0x2102                    |

|         |                   |      |     |         | QDC=3, rev 2.1 = 0x3201                    |

|        | IRQ (ROACK)         |    |    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|---------------------|----|----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6010 | irq_level           | 3  | RW | 0 | IRQ priority 17, 0 = IRQ off                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x6012 | irq_vector          | 8  | RW | 0 | IRQ return value                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x6014 | irq_test            | 0  | W  |   | initiates an IRQ (for test)                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x6016 | irq_reset           | 0  | W  |   | resets IRQ (for test)                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x6018 | irq_data_threshold  | 15 | RW | 1 | Every time the number of 32 bit words in the FIFO exceeds this threshold, an IRQ is emitted. Maximum allowed threshold is "FIFO size".                                                                                                                                                                                                                                                                                          |

| 0x601A | Max_transfer_data   | 15 | RW | 1 | <ol> <li>Specifies the amount of data read from FIFO before BERR is emitted. Only active for multi event mode 3.</li> <li>Transfer is stopped only after full events. Example: At Max_transfer_data = 1, 1 event per transfer is emitted.</li> <li>Specifies the number of events read from FIFO before BERR is emitted. Active for multi event mode 0xb.</li> <li>Setting the value to 0 allows unlimited transfer.</li> </ol> |

| 0x601C | IRQ_source          | 1  | RW | 1 | IRQ source: 0 = <b>event</b> threshold exceeded 1 = <b>data</b> threshold exceeded                                                                                                                                                                                                                                                                                                                                              |

| 0x601E | irq_event_threshold | 15 | RW | 1 | Every time the number of events in the                                                                                                                                                                                                                                                                                                                                                                                          |

|  |  | FIFO exceeds this threshold, an IRQ is |

|--|--|----------------------------------------|

|  |  | emitted.                               |

For multi event mode 2 and 3 the IRQ is:

- set when the FIFO fill level gets more than the threshold and is

withdrawn when IRQ is acknowledged or when the fill level goes below the threshold.

|        | MCST CBLT         |   |    |      |                      |

|--------|-------------------|---|----|------|----------------------|

| 0x6020 | cblt_mcst_control | 8 | RW | 0    | see table            |

| 0x6022 | cblt_address      | 8 | RW | 0xAA | A31A25 CBLT- address |

| 0x6024 | mcst_address      | 8 | R  | 0xBB | A31A25 MCST- address |

| Bit | Name     | Write                                              | Read                                                                 |

|-----|----------|----------------------------------------------------|----------------------------------------------------------------------|

| 7   | MCSTENB  | 1 Enable MCST<br>0 No effect                       | 0                                                                    |

| 6   | MCSTDIS  | 1 Disable MCST<br>0 No effect                      | 1 MCST enabled<br>0 MCST disabled                                    |

| 5   | FIRSTENB | 1 Enable first module in a CBLT chain 0 No effect  | 0                                                                    |

| 4   | FIRSTDIS | 1 Disable first module in a CBLT chain 0 No effect | 1 First module in a CBLT chain<br>0 Not first module in a CBLT chain |

| 3   | LASTENB  | 1 Enable last module in an CBLT chain 0 No effect  | 0                                                                    |

| 2   | LASTDIS  | 1 Disable last module in an CBLT chain 0 No effect | Last module in a CBLT chain     Not last module in a CBLT chain      |

| 1   | CBLTENB  | 1 Enable CBLT<br>0 No effect                       | 0                                                                    |

| 0   | CBLTDIS  | 1 Disable CBLT<br>0 No effect                      | 1 CBLT enabled<br>0 CBLT disabled                                    |

# **CBLT Address Field**

| A31A24    | A23                                                       |

|-----------|-----------------------------------------------------------|

| CBLT ADRS | 8 high bits, not significant + 16bit module address space |

# **MCST Address Field**

| A31A24   A23 | A00 |

|--------------|-----|

|--------------|-----|

| MCST ADRS | 8 high bits, not significant + 16bit module address space |

|-----------|-----------------------------------------------------------|

|-----------|-----------------------------------------------------------|

# At BLT32

When an empty module is accessed at address 0, BERR is emitted.

# At CBLT

When no module contains data, no data are transmitted. The last module emits BERR.

|        | FIFO handling      |    |    |   |                                                                                                                                                                                                                              |                                                                                                                  |                                                                                                    |

|--------|--------------------|----|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 0x6030 | buffer_data_length | 16 | R  |   | amount of data in FII<br>(only fully converted<br>Units → data_len_for<br>Can be used for sing                                                                                                                               | events).<br>mat.                                                                                                 | event transfer                                                                                     |

| 0x6032 | data_len_format    | 2  | RW | 2 | 0 = 8 bit, 1 = 16 bit, 2<br>4= show number of 6<br>The number of 32 bit<br>If necessary the fill w<br>For len 0 and 1 the m<br>when number exceed<br>FIFO is not affected.                                                   | = 32 bit, 3 = 6<br>events in FIFO.<br>t words is alwa<br>ord "0" is add<br>nax value 0xFF                        | 4 bit,<br>ays even.<br>ed.<br>FFF is shown                                                         |

| 0x6034 | readout_reset      |    | W  |   | At single event mode trigger, allow IRQ At multi event = 1: ch when enough data. A buffer fill level does reshold at readout At multievent = 3: cleareadout                                                                  | ecks threshol<br>Allows safe op<br>not go below t                                                                | d, sets IRQ<br>eration when<br>:he data                                                            |

| 0x6036 | multi event        | 4  | RW | 0 | Bit[3]                                                                                                                                                                                                                       | Bit[2]                                                                                                           | Bit[1:0]                                                                                           |

|        |                    |    |    |   | count events<br>not words<br>(reg. 0x601A)                                                                                                                                                                                   | skip berr,<br>send EOB                                                                                           | mode[1:0]                                                                                          |

|        |                    |    |    |   | Allow multi event but mode = 0 → no (0x60 conversion) mode = 1 → yes, unli reset required (0x603 readout). Don't use fi mode = 3 → yes but amount of data. With data words can be spreached, the next entransfer by emitting | mited transfe<br>34 can be writ<br>or CBLT<br>MDPP transfe<br>oreg 0x601A to<br>becified. After<br>d of event ma | r, no readout<br>ten after block<br>rs limited<br>the number of<br>word limits is<br>rk terminates |

|        |              |   |    |   | event by event transfer (Berr after each event). The next data block can be transferred after writing 0x6034 (resets Berr). |

|--------|--------------|---|----|---|-----------------------------------------------------------------------------------------------------------------------------|

|        |              |   |    |   | <b>Berr handling:</b> when bit[2] is set:<br>Send EOB = bit[31:30] = bx10 instead of Berr                                   |

|        |              |   |    |   | Bit[3]: Compare number of transmitted events (not words!) with max_transfer_data (0x601A) for Berr condition.               |

| 0x6038 | marking_type | 2 | RW | 0 | 00 → event counter<br>01 → time stamp<br>11 → extended time stamp                                                           |

|        |              |   |    |   | → next page                                                                                                                 |

| 0x603A | start_acq  | 1 | RW | 1 | 1 → start accepting triggers If no external trigger logic, which stops the gates when daq is not running, is implemented, this register should be set to 0 before applying the FIFO_reset to get a well defined status. When setting it to 1 again for data acquisition start, the module is in a well defined status. |

|--------|------------|---|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x603C | FIFO_reset |   | W  |   | Initialize FIFO                                                                                                                                                                                                                                                                                                        |

| 0x603E | data_ready | 1 | R  |   | 1 → data available                                                                                                                                                                                                                                                                                                     |

|        | operation mode |   |    |   |                                       |

|--------|----------------|---|----|---|---------------------------------------|

|        |                |   |    |   |                                       |

| 0x6042 | tdc_resolution | 3 | RW | 5 | 5 → 781 ps = 25 ns / 32               |

|        |                |   |    |   | 4 → 391 ps = 25 ns / 64               |

|        |                |   |    |   | 3 → 195 ps = 25 ns / 128              |

|        |                |   |    |   | 2 → 98 ps = 25 ns / 256               |

|        |                |   |    |   | 1 → 49 ps = 25 ns / 512               |

|        |                |   |    |   | 0 → 24 ps = 25 ns / 1024              |

| 0x6044 | output_format  | 2 | RW | 0 | 0 = standard window of interest mode. |

|        |                |   |    |   | from FW2050:                          |

|        |                |   |    |   | 4 = SCP only, compact Streaming mode  |

|        |                |   |    |   | 8 = standard streaming mode           |

|        |                |   |    |   | 16 = window of interest with samples  |

|        |                |   |    |   | 24 = standard streaming with samples. |

| 0x6046 | adc_resolution | 0 | RW | 0 | Always 16 bits                        |

| Trigger |  |  |  |  |

|---------|--|--|--|--|

|---------|--|--|--|--|

| 0x6050 | win_start                   | 15 | RW  | 16k-<br>16 | Unit: 25ns/16 = 1.56 ns<br>Start window of interest:<br>0x0000 start at -25.56us<br>0x7FFF start at +25.56us<br>0x4000 = 16k no delay                                                                                        |       |                                 |             |               |       |                    |      |

|--------|-----------------------------|----|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|-------------|---------------|-------|--------------------|------|

| 0x6054 | win_width                   | 14 | RW  | 32         | < 16 k,                                                                                                                                                                                                                      | windo | w starts<br>w is dela<br>max 16 | befo<br>yed |               |       |                    |      |

| 0x6058 | trig_source                 | 10 | KVV | 0x100      |                                                                                                                                                                                                                              |       |                                 |             |               |       | e wir              | ndow |

|        |                             |    |     |            | <b>Defines the trigger which creates the wind of interest</b> . This can be: one or both of the trigger inputs, any of the 16 channel inputs, or a logical "OR" of all channels.                                             |       |                                 |             |               | ,     |                    |      |

|        |                             |    |     |            | Whole<br>2 b                                                                                                                                                                                                                 |       |                                 | han<br>bits |               |       | i <b>g</b><br>oits |      |

|        |                             |    |     |            | RCP:<br>reset                                                                                                                                                                                                                | В0    | active                          | 0           | Chan<br>[3:0] | T1    | T0                 |      |

| 0x605A | trig_source_2<br>(SCP only) | 16 | RW  | 0          | When above register trig_source == 0, this register allows to set any number of individual channels creating the trigger.  Bit 0 corresponds to channel 0, bit 15 to channel 15. A "1" marks the channels as trigger source. |       |                                 |             |               | annel |                    |      |

| 0x605C | first_hit                   | 1  | RW  | 1          | l                                                                                                                                                                                                                            | _     | mit first                       |             | windov        | V     |                    |      |

| 0x605E | trigger_output              | 10 | RW  | 0x10<br>0  | 0 = transmit all hits in the window  Defines the trigger which creates the output trigger. This can be any of the 16 channel inputs, or a logical "OR" of all channels.                                                      |       |                                 |             |               |       | tput               |      |

|        |                             |    |     |            | Whole                                                                                                                                                                                                                        | bank  | 16 c                            | han         | nels          | 0     | 0                  |      |

|        |                             |    |     |            | 0                                                                                                                                                                                                                            | В0    | active                          | 0           | Chan<br>[3:0] | 0     | 0                  |      |

# Bank trigger source example

Trigger 0 starts the window: Channel 3 starts window: (bit 7 enables channel trigger) Whole bank 0 may start the window: bank0\_trig\_source = b00 0000 00 01 bank0\_trig\_source = b00 1000 11 00 bank0\_trig\_source = b01 0000 00 00

When whole bank is selected, the channel creating the trigger is the first to trigger, but random within 12.5ns.

| IO<br>0x6060 | Inputs, outputs |   |    |      |                                               |

|--------------|-----------------|---|----|------|-----------------------------------------------|

| 0x6060       | ECL3            | 8 | RW | 0x00 | INPUT                                         |

|              |                 |   |    |      | lower 4 bit: 0= Off, 1= Trig0 in              |

|              |                 |   |    |      | higher 4 bit: 0 = terminated, 1= unterminated |

| 0x6062 | ECL2 | 8 | RW | 0x00 | INPUT                                         |

|--------|------|---|----|------|-----------------------------------------------|

|        |      |   |    |      | lower 4 bit: 0= Off, 1= Sync_in, 2= Trig1 in  |

|        |      |   |    |      | higher 4 bit: 0 = terminated, 1= unterminated |

|        |      |   |    |      | when sync is selected also set reg 0x6096 !!  |

| 0x6064 | ECL1 | 8 | RW | 0x00 | INPUT                                         |

|        |      |   |    |      | lower 4 bit: 0= Off, 1= Reset_in              |

|        |      |   |    |      | higher 4 bit: 0 = terminated, 1= unterminated |

| 0x6066 | ECL0 | 4 | RW | 0    | OUTPUT                                        |

|        |      |   |    |      | 0 = Off, 4 = Busy,                            |

|        |      |   |    |      | 8 = data in buffer above threshold 0x6018     |

|        |      |   |    |      | (= Data ready)                                |

|        |      |   |    |      | 9 = events in buffer above threshold 0x601E   |

| 0x6068 | NIM4 | 2 | RW | 1    | INPUT                                         |

|        |      |   |    |      | 0 = Off, 1= Trig0_in                          |

| 0x606A | NIM3 | 2 | RW | 1    | 0, 1 = Off, 2 = Sync in                       |

|        |      |   |    |      | when sync is selected also set reg 0x6096 !!  |

| 0x606C | NIM2 | 2 | RW | 1    | 0 = Off, and 1 = Trig1_in, 2 = Reset          |

| 0x606E | NIM1 |   |    |      | always Trig_out                               |

|        |      |   |    |      |                                               |

| 0x6070 | Test pulser      |    |    |     |                                                   |

|--------|------------------|----|----|-----|---------------------------------------------------|

| 0x6070 | pulser_status;   | 1  | RW | 0   | 0 = Off, 1 = On                                   |

|        |                  |    |    |     | (fixed frequency of about 1.6kHz)                 |

|        |                  |    |    |     | Degrades the input signals, so only use for test. |

|        |                  |    |    |     | Rise time 10ns, decay time 102.4us                |

| 0x6072 | pulser_amplitude | 12 | RW | 400 | maximum amplitude: 0xFFF = 4095                   |

|        |                  |    |    |     | Max value corresponds to about 30% at gain=1.     |

|        |                  |    |    |     | Gain jumpers are situated before pulser           |

|        |                  |    |    |     | coupling, so have no effect on the pulser         |

|        |                  |    |    |     | amplitude.                                        |

|        |                  |    |    |     |                                                   |

| 0x6074 | NIM0             | 4  | RW | 1   | 0= Off, 1= Cbus,                                  |

|        |                  |    |    |     | 4 = Busy_out (= FIFO full or ACQ stopped)         |

|        |                  |    |    |     | 8 = data in buffer above threshold 0x6018         |

|        |                  |    |    |     | 9 = events in buffer above threshold 0x601E       |

| 0x607A | monitor_on       | 1  | RW | 0   | switch monitor on                                 |

| 0x607C | set_mon_channel  | 4  | RW | 0   | set channel to monitor                            |

| 0x607E | set_wave         | 2  | RW | 0   | set wave for to monitor                           |

#### **IO** selection Overview

The numbers in the table can be written to the corresponding register. For example: ECL2 should input the trigger 1: write 2 to 0x6062.

The **monitor outputs at NIM2 and NIM3** always override the register setting when they are activated by the front panel switch. When acquisition is started (0x603A), NIM2 and NIM3 fall back to their register values. But they can be reactivated by the front panel switches.

| Ю    | default | TR0 | TR1 | SYN | RES | TRout | Busy | Rdy<br>data | Rdy<br>event | Cbus |

|------|---------|-----|-----|-----|-----|-------|------|-------------|--------------|------|

| ECL3 | 0       | 1   |     |     |     |       |      |             |              |      |

| ECL2 | 0       |     | 2   | 1   |     |       |      |             |              |      |

| ECL1 | 0       |     |     |     | 1   |       |      |             |              |      |

| ECL0 | 0       |     |     |     |     |       | 4    | 8           | 9            |      |

| NIM4 | 1       | 1   |     |     |     |       |      |             |              |      |

| NIM3 | 1       |     |     | 2   |     |       |      |             |              |      |

| NIM2 | 1       |     | 1   |     | 2   |       |      |             |              |      |

| NIM1 | 1       |     |     |     |     | 1     |      |             |              |      |

| NIM0 | 1       |     |     |     |     |       | 4    | 8           | 9            | 1    |

Selection of 0 always means it is unused or "Off"

# **Description**

TR0 = Trigger 0 input

TR1 = Trigger 1 input

SYN = external Frequency to synchronise event time stamp

RES = reset for event time stamp

TRout = trigger output

Mon0 = analog output to monitor internal filtered signals, noise, Pole zero

Mon1 = analog output to monitor internal filtered signals, noise, Pole zero

Busy = module not ready to take more triggers

Rdy dat = data in buffer above threshold register "0x6018"

Rdy eve = events in buffer above threshold register "0x601E"

Cbus = control bus to control external mesytec modules (MHV-4, MPRB-32...)

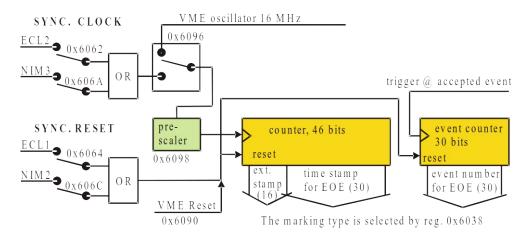

# **CTRA**

Time stamp counters, event counters

# All counters have to be read in the order: low word then high word !!!

They are latched at low word read. The event counter counts events which are written to the buffer.

| CTRA   | counters A    |    |    |     |                                                     |

|--------|---------------|----|----|-----|-----------------------------------------------------|

| 0x6090 |               |    |    |     |                                                     |

| 0x6090 | Reset_ctr_ab  | 2  | RW |     | b0001 resets all counters in CTRA,                  |

|        |               |    |    |     | b0010 resets all counters in CTRB,                  |

|        |               |    |    |     | b1100 allows single shot reset for CTRA             |

|        |               |    |    |     | with first edge of external reset signal.           |

|        |               |    |    |     | the bit bx1xx is reset with this first edge         |

|        |               |    |    |     |                                                     |

|        |               |    |    |     | Reset of "counters A" will also reset the global 46 |

|        |               |    |    |     | bit TDC time stamp                                  |

| 0x6092 | evctr_lo      | 16 | R  | 0   | event counter low value                             |

| 0x6094 | evctr_hi      | 16 | R  | 0   | event counter high value                            |

| 0x6096 | ts_sources    | 5  | RW | b00 | [ext_reset, frequency_source]                       |

|        |               |    |    |     | bit0: frequency source (VME=0, external=1)          |

|        |               |    |    |     | bit1: external reset enable = 1                     |

|        |               |    |    |     | RCP, QDC: bit4: CTRB "time" counts trigger          |

|        |               |    |    |     | outputs (= free triggers, selected by 0x605E)       |

| 0x6098 | ts_divisor    | 16 | RW | 1   | time stamp = time / ( ts_divisor)                   |

|        |               |    |    |     | 0 means division by 65536                           |

| 0x609C | ts_counter_lo | 16 | R  |     | Time low value                                      |

| 0x609E | ts_counter_hi | 16 | R  |     | Time high value                                     |

# **CTRB**

Counters are latched when VME is reading the low word Output value is divided by 40 to give a 1 us time basis

| CTRB   | counters B |    |   |   |                                              |

|--------|------------|----|---|---|----------------------------------------------|

| 0x60A0 |            |    |   |   |                                              |

| 0x60A8 | time_0     | 16 | R |   | Time [1 us] (48 bit)                         |

|        |            |    |   |   | RCP: alternately: free triggers, selected by |

|        |            |    |   |   | 0x6096 bit4, and 0x605E                      |

| 0x60AA | time_1     | 16 | R |   |                                              |

| 0x60AC | time_2     | 16 | R |   |                                              |

| 0x60AE | stop_ctr   | 2  | W | 0 | 0 = run, 1= stop counter                     |

|        |            |    |   |   | bit 0 all counter B                          |

|        |            |    |   |   | bit 1 time stamp counter (A)                 |

# **Channel addressing for parameter setting**

| 0x6100 | select_chan_pair | 4 | RW | 8 | channel to be modified:                 |

|--------|------------------|---|----|---|-----------------------------------------|

|        |                  |   |    |   | 07 channel pairs;                       |

|        |                  |   |    |   | chan $0,1 = 0$ ,                        |

|        |                  |   |    |   | chan $2,3 = 1,$                         |

|        |                  |   |    |   | 8 = all channels (set to common values) |

User Channel setting for a channel pair, software module "RCP" and "SCP" \*\*\* After writing a register in this page, 20us wait time is required \*\*\*\*\*

Parameters "threshold" and "PZ" are for individual channels, so two parameters per pair. When channels are all set simultaneously (0x6100 = 8) the "lower channel" parameter codes for even (0,2,4,6..), the "upper channel" parameter for odd (1,3,5,7...)

| Address | Parameter.           |    |    | default | Comment                                                                                                                                                                                                                                                                 |

|---------|----------------------|----|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6110    | TF_int_diff:         | 7  | RW | 20      | All times are in multiples of 12.5 ns. Common for 2 channels TF- integration/differentiation time, chan 0/1 valid values 1125 (12.5 (15) ns to 1.6 us)                                                                                                                  |

| 611A    | Gain:                | 15 | RW | 2000    | common for 2 channels, gain x 100<br>gain 1200, chan 0/1; setting 100 (gain=1) 19000<br>(gain = 200)                                                                                                                                                                    |

| 611C    | threshold0:          | 16 | RW | 0xff    | 0 to 64k (65535). 64 k corresponds to full range. sets lower channel (ex. chan4 when pair 2 is selected)                                                                                                                                                                |

| 611E    | threshold1           | 16 | RW | 0xff    | sets upper channel (ex. chan5 when pair 2 is selected)                                                                                                                                                                                                                  |

| 0x6120  |                      |    |    |         |                                                                                                                                                                                                                                                                         |

| 6124    | Shaping_time         | 11 | RW | 160     | common for 2 channels, FWHM-width values 41999 (= 50 ns to 25 us)                                                                                                                                                                                                       |

| 6126    | BLR                  | 2  | RW | 2       | common for 2 channels, Base line restorer setting, 0 = off, 1 = strict (int. time = 4 shaping times), 2 = soft (int. time = 8 shaping times) 3 = very strict (int. time = 1 shaping time)                                                                               |

| 6128    | reset_time           |    | RW | 1000    | common for 2 channels (min 16 = 200ns)                                                                                                                                                                                                                                  |

| 612A    | signal_rise_<br>time | 7  | RW | 80      | common for 2 channels -default = 0, for Si-detectors, constant rise time detectors -> shortest dead time -for germanium detectors with position dependent rise time, set to largest signal rise time. This results in highest resolution and ballistic loss correction. |

# For SCP only, (not for RCP firmware )

| 6112   | PZ0:          | 16 | RW | 0xffff | signal decay_time0, lower channel (for PZ compensation) valid: 6464k (65535), 0.8 us to 800 us, and infinite                                                                                     |

|--------|---------------|----|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6114   | PZ1:          | 16 | RW | 0xffff | signal decay_time1, upper channel                                                                                                                                                                |

| 0x6146 | pre_samples   | 10 | RW | 4      | 01000, samples before trigger                                                                                                                                                                    |

| 0x6148 | tot_samples   | 10 | RW | 12     | 01000, total number of samples                                                                                                                                                                   |

| 0x614A | sample_config | 8  | RW | 0      | {no_offset_corr, no_resamp,0,0,0,0,source[1:0]} source source = 0 Samples directly from ADC source = 1 Samples reconstructed input source = 2 Samples from TF-int source = 3 Samples from Shaper |

# How to set channel parameters

**TF\_int\_diff** is the integration and differentiation time for the timing filter.

It must not be set to a higher value than the shaping time!

- 1) If the timing resolution has to optimised, the integration time should be set to the rise time.

- 2) If a very low threshold is required, it may be necessary to set it to a larger value than the rise time, maximum value is 127 (=1.6us) or the shaping time.

**PZ0 / PZ1:** (not required for reset preamps "RCP") decay time of the pulse. The parameter must be very precise to minimise under- or overshoot of the shaped signal. The value is usually not known very precise, so it is easiest way to minimise the under- or overshoot with the monitor signals (select Tmon 3). An automatic adjust run is under consideration. Example: the decay time is 25us (time the signal needs from 100% to 36.8%) so the set value is 25000/12.5 = 2000.

**Gain:** The gain can be set in 1% steps. The resulting range (input voltage for highest channel in the spectrum) can be calculated as: Range = Gain\_Jumper\_Range / Gain. For example: Gain-jumper with 3V label, Gain setting = 1000 -> Gain = 10, so maximum signal will be 0.3V.

# **threshold0 / 1:** Threshold setting, 64k is full range.

The threshold is required to detect a signal out of the noise. The threshold also signals an approximated noise level to the BLR.

Example: for a low noise application the noise is 1E-3 of the full range. Setting the threshold to 3x noise this results in a set value of 64k\*1E-3\*3 = 197.

**Shaping\_time:** is the integration time of the shaping filter. The shaping is triangular, the shaping time corresponds to the width of the pulse at half maximum (FWHM).

Compared to the traditional "shaping time" the FWHM is about a factor of 2 longer.

Example: the traditional shaping time should be 1us, the FWHM shaping time has to be set to 2us, this results in a set value of 2000/12.5 = 160;

#### **BLR:** can be set to

- 0: off

- 1: soft, may have slight advantages for very low noise signals

- 2: default, compensates also for faster baseline deviations.

**reset:** additional time the channel is reset at an overflow. The total reset time is: shaping time + reset. The default value of 16 is the shortest possible value, and usually need not to be modified.

**signal\_rise\_ time:** Default = 0; only needed for detectors with large rise time variation, when the rise time is in the order of magnitude of the shaping time, and when high amplitude resolution is required. This parameter increases the flat top of the shaping pulse. Allows for ballistic loss correction when set to the largest possible rise time. Example: radial germanium detector with maximum 250 ns rise time. Set this parameter to 20.

# **Special Trigger outputs**

Starting with March 2021 a new feature is built into all firmware. The VME IRQ lines are mostly unused, but are very good high quality lines to the VME controller. A combination of input triggers can be sent to the 7 available IRQ lines, and can be processed in the Triger IO of the MVLC controller. A collision of signals with other IRQ signaling of the module should be avoided. Several modules may control the same IRQ line, the outputs are then a wired OR of all participating modules. Pulse length is fixed 50ns.

| VME-<br>Addr | Name         | Width | Directi<br>on | Value  | Description                                                                                                                                           |

|--------------|--------------|-------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6300       | Trig to IRQ1 | 16    | RW            | 0x0000 | Connect an OR of the selected channel triggers (up to 16) to IRQ line 1. Example 0b00000000 10000001 means channel 0 and 7 are Ored and sent to IRQ 1 |

| 0x6304       | Trig to IRQ2 | 16    | RW            | 0x0000 |                                                                                                                                                       |

| 0x6308       | Trig to IRQ3 | 16    | RW            | 0x0000 |                                                                                                                                                       |

| 0x630C       | Trig to IRQ4 | 16    | RW            | 0x0000 |                                                                                                                                                       |

| 0x6310       | Trig to IRQ5 | 16    | RW            | 0x0000 |                                                                                                                                                       |

| 0x6314       | Trig to IRQ6 | 16    | RW            | 0x0000 |                                                                                                                                                       |

| 0x6318       | Trig to IRQ7 | 16    | RW            | 0x0000 |                                                                                                                                                       |

# **Data handling**

The event buffer is organized as a FIFO with a depth of 64 k x 32 bit.

Data is organized in an event structure, maximum size of one event is 255x 32-bit words (Header, End of event, 251 data, extended time stamp, fill word).

#### **Event structure**

| Word # (32 bit) | Content                                                |

|-----------------|--------------------------------------------------------|

| 0               | Event header (indicates # of n following 32-bit words) |

| 1               | Data word #1                                           |

| 2               | Data word #2                                           |

|                 |                                                        |

| n-1             | Data word #n-1                                         |

| n               | End of event marker                                    |

# Event Header (4 byte, 32 bit)

| Sh | ort  | #1         |    |    |     |    |    |    |      |            |     |     |    |    |    | Sh  | ort | #0         |    |      |    |   |   |    |      |            |     |    |     |   |   |

|----|------|------------|----|----|-----|----|----|----|------|------------|-----|-----|----|----|----|-----|-----|------------|----|------|----|---|---|----|------|------------|-----|----|-----|---|---|

| Ву | te # | <b>#</b> 3 |    |    |     |    |    | Ву | te # | <b>‡</b> 2 |     |     |    |    |    | Ву  | te# | <b>‡</b> 1 |    |      |    |   |   | Ву | te # | <b>‡</b> 0 |     |    |     |   |   |

| 31 | 30   | 29         | 28 | 27 | 26  | 25 | 24 | 23 | 22   | 21         | 20  | 19  | 18 | 17 | 16 | 15  | 14  | 13         | 12 | 11   | 10 | 9 | 8 | 7  | 6    | 5          | 4   | 3  | 2   | 1 | 0 |

| h  | sig  |            | su | bh | ead | er |    |    |      | m          | odı | ule | id |    |    | tdo | re  | s          | a  | dc r | es | l | # | of | foll | ow         | ing | wo | rds |   |   |

| 0  | 1    | 0          | 0  | х  | х   | х  | х  | ii | ii   | ii         | ii  | ii  | ii | ii | ii | t   | t   | t          | а  | а    | а  | n | n | n  | n    | n          | n   | n  | n   | n | n |

hsig: header signature = b01

subheader id: currently = b00xxx  $\rightarrow$  Byte #3 = 0x40

module id: depending on board coder settings → Byte #2 = Module

ID

tdc res: TDC resolution, depending on register 0x6042

adc res: ADC resolution, depending on register 0x6042

# of follow. words: indicates amount n of following 32-bit words:

n-1 events + 1 end of event marker)

# Data words (4 byte, 32 bit) DATA-event

| Sh | ort  | #1 |    |    |    |    |    |      |      |            |    |     |    |      |    | Sh | ort  | #0         |    |    |    |      |    |      |     |            |   |   |   |   |   |

|----|------|----|----|----|----|----|----|------|------|------------|----|-----|----|------|----|----|------|------------|----|----|----|------|----|------|-----|------------|---|---|---|---|---|

| Ву | te # | #3 |    |    |    |    |    | Ву   | te # | <b>‡</b> 2 |    |     |    |      |    | Ву | te # | <b>‡</b> 1 |    |    |    |      |    | Ву   | te# | <b>‡</b> 0 |   |   |   |   |   |

| 31 | 30   | 29 | 28 | 27 | 26 | 25 | 24 | 23   | 22   | 21         | 20 | 19  | 18 | 17   | 16 | 15 | 14   | 13         | 12 | 11 | 10 | 9    | 8  | 7    | 6   | 5          | 4 | 3 | 2 | 1 | 0 |

| ds | sig  | fi | x  |    |    |    | 1  | flag | JS   | Т          |    | cha | nn | el # |    |    |      |            |    |    | da | ta ( | 16 | vali | d b | its)       |   |   |   |   |   |

| 0  | 0    | 0  | 1  | х  | х  | х  | х  | р    | О    | t          | С  | С   | С  | С    | С  | d  | d    | d          | d  | d  | d  | d    | d  | d    | d   | d          | d | d | d | d | d |

|    |      |    |    |    |    |    |    |      |      |            |    |     |    |      |    |    |      |            |    |    |    |      |    |      |     |            |   |   |   |   |   |

dsig: data signature = b00

fix: bit field marking a data word = b0001xxxx  $\rightarrow$  Byte #3 = 0x1x

(extended time stamp marked as = b0010xxxx)

pu: pile up detected

ov: overflow or underflow

T: T = 1: Trigger channel,  $\{T, chan\#\} = 32$  for trig0, or = 33 for trig1

channel #: T = 0: channel # runs from 0 to 15 for amplitudes, 16 to 31 for time.

within an event buffer, channels may occur in arbitrary order

data: conversion data, data width up to 16 valid bits

#### End of Event mark (4 byte, 32 bit)

| Sh | ort   | #1         |                                          |   |  |  |  |    |     |            |    |     |      |    |     | Sh  | ort  | #0   |    |      |      |    |   |    |      |    |   |   |   |  |  |

|----|-------|------------|------------------------------------------|---|--|--|--|----|-----|------------|----|-----|------|----|-----|-----|------|------|----|------|------|----|---|----|------|----|---|---|---|--|--|

| Ву | rte # | <b>‡</b> 3 |                                          |   |  |  |  | Ву | te# | <b>‡</b> 2 |    |     |      |    |     | Ву  | te # | ŧ1   |    |      |      |    |   | Ву | te # | ŧ0 |   |   |   |  |  |

| 31 | 30    | 29         | 29 28 27 26 25 24 23 22 21 20 19 18 17 1 |   |  |  |  |    |     |            |    | 16  | 15   | 14 | 13  | 12  | 11   | 10   | 9  | 8    | 7    | 6  | 5 | 4  | 3    | 2  | 1 | 0 |   |  |  |

| es | sig   |            |                                          |   |  |  |  |    |     |            | tr | igg | er o | ou | nte | r/t | ime  | e st | am | p (3 | 30bi | t) |   |    |      |    |   |   |   |  |  |

| 1  | 1     | t          | t                                        | t |  |  |  |    |     |            |    |     | t    | t  | t   | t   | t    | t    | t  | t    | t    | t  | t | t  | t    | t  | t | t | t |  |  |

esig: end of event signature = b11