Detector Readout Systems

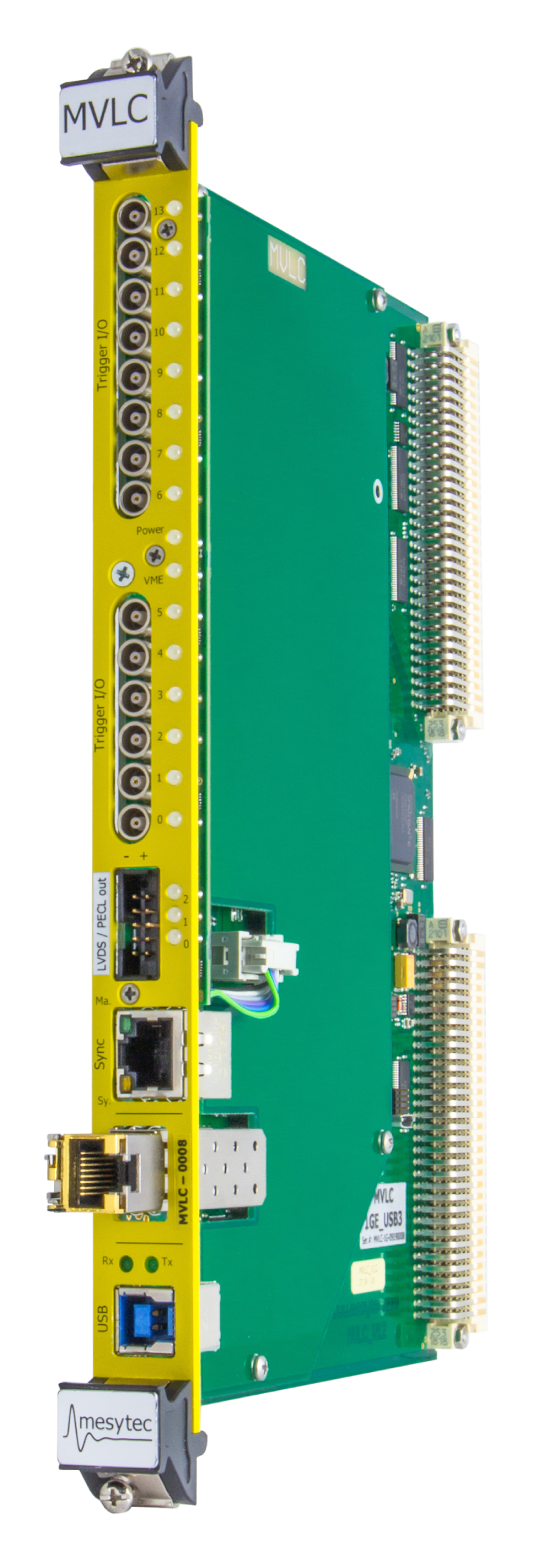

The mesytec MVLC is a modern, FPGA-based VME Controller enabling VME module

readout at high trigger and data rates. VME bus signalling and internal command processing have

been optimized to achieve low latency readouts. An integrated logic module enables flexible

setup of the NIM I/Os and ECL outputs and allows to define custom trigger conditions using

internal logic blocks.

Features

- Low-latency, low-deadtime VME module readout

- Handles high data and triggers rates

- 127 MB/s sustained transfer rate via USB3 ( event rate of 1MHz, event length of 104-120 bytes)

- Full utilisation of GBit Ethernet bandwidth

- Flexible Trigger and I/O logic module

- USB3, USB2 and GBit/s Ethernet connectivity

- Onboard SFP cage allows using copper or fiber based Ethernet

- Supported by the mvme software package

- Open-source, user-space driver and utility library for building readout systems. Usable from C++/C.

Firmware update instructions can be found here, the latest firmware file is available here.

Documentation and code examples

For details about the builtin Trigger/IO module refer to the

mvme documentation.

Programming examples for the mesytec-mvlc driver library are

available on github.

© 2025 mesytec GmbH & Co. KG